The Best Touch Sensor Solution!

# LOW POWER OR

# GREENCHIP

# **GreenTouch**3LP<sup>™</sup> GTX314L **Capacitive** Touch Sensor

DATASHEET VER6.01

www.greenchip.co.kr

# **Important Notice**

#### COPYRIGHT © 2009 BY GREENCHIP INC. - ALL RIGHTS RESERVED.

GREENCHIP OWNS ALL RIGHT, TITLE AND INTEREST IN THE PROPERTY AND PRODUCTS DESCRIBED HEREIN, UNLESS OTHERWISE INDICATED. NO PART OF THIS DOCUMENT MAY BE TRANSLATED TO ANOTHER LANGUAGE OR PRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY INFORMATION STORAGE AND RETRIEVAL SYSTEM WITHOUT WRITTEN PERMISSION FROM GREENCHIP.

GREENCHIP RESERVES THE RIGHT TO CHANGE PRODUCTS AND SPECIFICATIONS WITHOUT WRITTEN NOTICE. CUSTOMERS ARE ADVISED TO OBTAIN THE LATEST VERSIONS OF ANY PRODUCT SPECIFICATIONS.

GREENCHIP MAKES NO WARRANTIES, EXPRESSED OR IMPLIED, OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OTHER THAN COMPLIANCE WITH THE APPLICABLE GREENCHIP SPECIFICATION SHEET FOR THE PRODUCT AT THE TIME OF DELIVERY. IN NO EVENT SHALL GREENCHIP BE LIABLE FOR ANY INDIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES AS A RESULT OF THE PRODUCT'S PERFORMANCE OR FAILURE TO MEET ANY ASPECT OF SUCH SPECIFICATION.

GREENCHIP PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN LIFE SUPPORT APPLIANCES, DEVICES OR SYSTEMS WHERE A

MALFUNCTION OF A GREENCHIP DEVICE COULD RESULT IN A PERSONAL INJURY OR LOSS OF LIFE. CUSTOMERS USING OR SELLING GREENCHIP

DEVICES FOR USE IN SUCH APPLICATIONS DO SO AT THEIR OWN RISK AND AGREE TO FULLY INDEMNIFY GREENCHIP FOR ANY DAMAGES

RESULTING FROM SUCH IMPROPER USE OR SALE.

INFORMATION CONTAINED HEREIN IS PRESENTED ONLY AS A GUIDE FOR THE APPLICATIONS OF OUR PRODUCTS. GREENCHIP DOES NOT WARRANT THIS PRODUCT TO BE FREE OF CLAIMS OF PATENT INFRINGEMENT BY ANY THIRD PARTY AND DISCLAIMS ANY WARRANTY OR INDEMNIFICATION AGAINST PATENT INFRINGEMENT. NO RESPONSIBILITY IS ASSUMED BY GREENCHIP FOR ANY PATENT INFRINGEMENT RESULTING FROM USE OF ITS PRODUCTS BY THEMSELVES OR IN COMBINATION WITH ANY OTHER PRODUCTS.

NO LICENSE IS HEREBY GRANTED BY IMPLICATION OR OTHERWISE UNDER ANY PATENT OR PATENT RIGHTS OF GREENCHIP.

THE GREENCHIP LOGO IS A REGISTERED TRADEMARK OF GREENCHIP. THE GreenTouch $3LP^{TM}$  IS A REGISTERED TRADEMARK OF GREENCHIP.

www.greenchip.co.kr

# **Table of Contents**

| 1. | INTRODUCTION                                             |    |

|----|----------------------------------------------------------|----|

| 2. | FEATURES                                                 | 5  |

| 3. | BLOCK DIAGRAM                                            |    |

| 4. | APPLICATIONS                                             | 5  |

| 5. | ORDERING INFORMATION                                     | 5  |

| 6. | MARKING INFORMATION                                      | 5  |

| 7. | PIN DESCRIPTION                                          | 6  |

|    | 7.1 PACKAGE INFORMATION (QFN-24L PACKAGE)                | 6  |

|    | 7.2 PIN CONFIGURATION                                    |    |

| 8. | FUNCTION DESCRIPTION                                     | 8  |

|    | 8.1 INTERNAL AND EXTERNAL RESET (NRST)                   | 8  |

|    | 8.2 IMPLEMENTATION FOR TOUCH SENSING (SIN1 ~ SIN14, RIN) |    |

|    | 8.3 IMPLEMENTATION FOR INTERRUPT (INT)                   |    |

|    | 8.4 CTRL OPTION SELECTION (CTRL)                         |    |

|    | 8.5 I2C INTERFACE (SCL, SDA, CTRL)                       |    |

|    | 8.5.1 DEVICE ADDRESSING                                  |    |

|    | 8.5.2 READ OPERATION                                     | 14 |

|    | 8.5.3 WRITE OPERATION                                    |    |

| 9. | REGISTER DESCRIPTION                                     | 15 |

|    | 9.1 QUICK REGISTER MAP                                   | 15 |

|    | 9.2 REGISTER CONFIGURATION                               | 18 |

|    | 9.2.1 01H REGISTER                                       |    |

|    | 9.2.2 02H, 03H REGISTER                                  |    |

|    | 9.2.3 04H, 05H REGISTER                                  | 19 |

|    | 9.2.4 0AH REGISTER                                       | 20 |

|    | 9.2.5 0BH REGISTER                                       | 20 |

|    | 9.2.6 0CH REGISTER                                       | 21 |

|    | 9.2.7 0FH REGISTER                                       | 21 |

|    | 9.2.8 10H REGISTER                                       | 22 |

|     | 9.2.9 11H REGISTER                        | 23 |

|-----|-------------------------------------------|----|

|     | 9.2.10 13H REGISTER                       | 24 |

|     | 9.2.11 14H REGISTER                       | 25 |

|     | 9.2.12 15H REGISTER                       | 25 |

|     | 9.2.13 17H REGISTER                       |    |

|     | 9.2.14 18H REGISTER                       |    |

|     | 9.2.15 19H REGISTER                       |    |

|     | 9.2.16 20H~2DH REGISTER                   |    |

| 10. | ELECTRICAL CHARACTERISTICS                | 29 |

|     | 10.1 ABSOLUTE MAXIMUM RATINGS             | 29 |

|     | 10.2 I/O ELECTRICAL CHARACTERISTICS       | 30 |

|     | 10.3 RESET CHARACTERISTICS                | 32 |

|     | 10.4 INTERRUPT OUTPUT CHARACTERISTICS     | 32 |

|     | 10.5 SENSING INPUT CHARACTERISTICS        | 32 |

|     | 10.6 SYSTEM CHARACTERISTICS               | 33 |

|     | 10.7 I2C INTERFACE TIMING CHARACTERISTICS | 34 |

|     | 10.8 ESD CHARACTERISTICS                  | 35 |

|     | 10.9 LATCH-UP CHARACTERISTICS             | 35 |

| 11. | APPLICATION                               | 36 |

|     | 11.1 EXAMPLE CIRCUIT (QFN-24L PACKAGE)    | 36 |

|     | 11.2 APPLICATION NOTES                    |    |

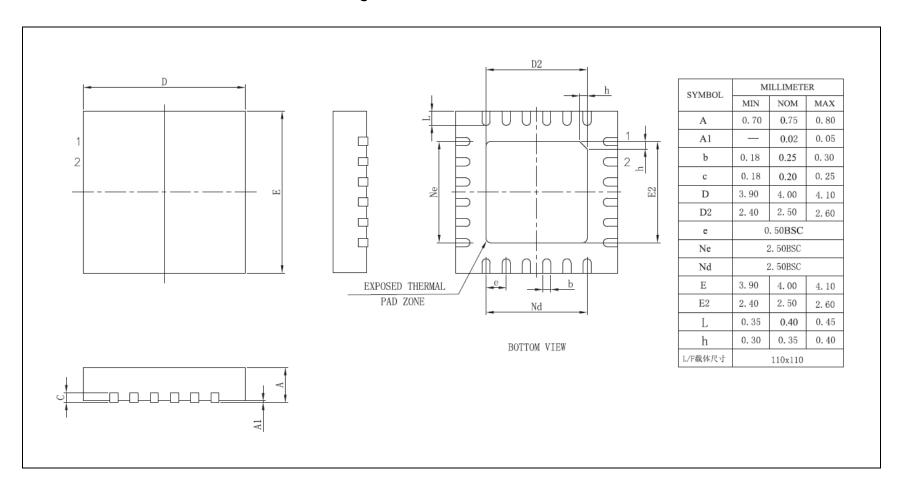

| 12. | PACKAGE DIMENSION (QFN-24L PACKAGE)       | 39 |

|     | • •                                       |    |

#### ${f 1}$ . INTRODUCTION

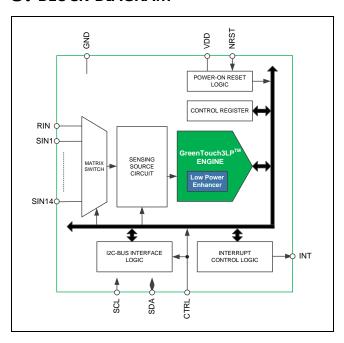

The GTX314L is one of the GreenTouch3LP™ capacitive touch sensor series. Especially the GTX314L can do capacitance sensing with 14 channels under above GreenTouch3LP™ engine operation. Thanks to the GreenTouch3LP™ low power engine, a variety of battery powered applications can increase product usage time. Also based on the technology of the existing GreenTouch3™ engine, reliability can be secured against various noise and environmental changes.

The internal control registers are readable and writable using I2C interface.

The GTX314L can be applied under wide supply voltage range from 1.8V to 5.5V. The CTRL pin of the GTX314L provides switchable chip ID that make a couple of chip parallel operations on the same I2C bus.

#### 2. FEATURES

- 14 channels cap. sensing input

- Embedded GreenTouch3LP<sup>TM</sup> Engine

- Analog compensation circuit

- Embedded digital noise filter

- Intelligent sensitivity calibration

- Low power enhancer

- I2C interface support

- Provide interrupt function

- Provide slide mode

- Provide "REGISTER WRITING LOCK" function

- Wide supply voltage range: 1.8V to 5.5V

- Single supply operation

- Package type

- QFN-24L (4.00x4.00x0.75,e=0.50)

- RoHS compliant

#### 3. BLOCK DIAGRAM

#### 4. APPLICATIONS

- Multi key application Door lock, Remote controller and Etc.

- Portable Electronics Mobile phone, MP3, PMP, PDA, Navigation, Digital Camera, Video Camera and Etc.

- Multimedia Devices Digital photo frame, Home theater system and Etc.

#### 5. ORDERING INFORMATION

| Part No.   | Package                         |

|------------|---------------------------------|

| GTX314L-QN | QFN-24L (4.00x4.00x0.75,e=0.50) |

### **6.** MARKING INFORMATION

# 7. PIN DESCRIPTION

This section describes the pin names and pin functions of GTX314L. Pinout configuration also illustrated as below. The GTX314L device is available in the following packages.

#### 7.1 PACKAGE INFORMATION (QFN-24L PACKAGE)

#### 7.2 PIN CONFIGURATION

| No. | Name  | Туре  | Description                                  |  |  |  |  |

|-----|-------|-------|----------------------------------------------|--|--|--|--|

| 1   | VDD   | PWR   | Supply Voltage                               |  |  |  |  |

| 2   | SIN1  | AO    | Channel 1: Touch sensing input               |  |  |  |  |

| 3   | SIN2  | AO    | Channel 2: Touch sensing input               |  |  |  |  |

| 4   | SIN3  | AO    | Channel 3: Touch sensing input               |  |  |  |  |

| 5   | SIN4  | AO    | Channel 4: Touch sensing input               |  |  |  |  |

| 6   | SIN5  | AO    | Channel 5: Touch sensing input               |  |  |  |  |

| 7   | SIN6  | AO    | Channel 6: Touch sensing input               |  |  |  |  |

| 8   | SIN7  | AO    | Channel 7: Touch sensing input               |  |  |  |  |

| 9   | SIN8  | AO    | Channel 8: Touch sensing input               |  |  |  |  |

| 10  | SIN9  | AO    | Channel 9: Touch sensing input               |  |  |  |  |

| 11  | SIN10 | AO    | Channel 10: Touch sensing input              |  |  |  |  |

| 12  | N.C   | -     | -                                            |  |  |  |  |

| 13  | SIN11 | AO    | Channel 11: Touch sensing input              |  |  |  |  |

| 14  | SIN12 | AO    | Channel 12: Touch sensing input              |  |  |  |  |

| 15  | SIN13 | AO    | Channel 13: Touch sensing input              |  |  |  |  |

| 16  | SIN14 | AO    | Channel 14: Touch sensing input              |  |  |  |  |

| 17  | GND   | GND   | Ground connection                            |  |  |  |  |

| 18  | RIN   | AO    | Capacitance reference input                  |  |  |  |  |

| 19  | NRST  | DI    | Reset control pin (Active LOW)               |  |  |  |  |

| 20  | N.C   | -     | -                                            |  |  |  |  |

| 21  | CTRL  | AO/DI | CTRL Option (Refer to CTRL OPTION SELECTION) |  |  |  |  |

| 22  | SCL   | DI    | I2C serial clock input                       |  |  |  |  |

| 23  | SDA   | DIO   | I2C serial data communication pin            |  |  |  |  |

| 24  | INT   | DO    | Interrupt output pin                         |  |  |  |  |

**NOTE:** DI: Digital Input, DO: Digital Output, DIO: Digital Input and Output, AI: Analog Input, AO: Analog Output, PWR: POWER

#### 8. FUNCTION DESCRIPTION

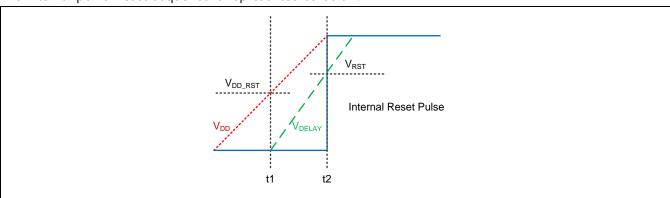

#### 8.1 INTERNAL AND EXTERNAL RESET (NRST)

The GTX314L has both internal power-on reset and external reset functions. The internal reset operation is used for initial power-on reset and the external reset operation is done by NRST pin.

Low pulse signal by NRST pin is for an abrupt reset which is required for intensive system reset. The NRST pin might be floating and no external reset components are required when the external reset is not in use.

The internal power reset sequence is represented as below.

The internal  $V_{DELAY}$  voltage starts to rise when VDD come up to  $V_{DD\_RST}$  level. The internal reset pulse is maintained as low between t1 and t2. During this low pulse period, the internal power reset operation is finished. Every time when VDD drops under  $V_{DD\_RST}$  internal reset block makes  $V_{DELAY}$  signal low and then internal reset pulse drops to low. By above internal reset operation sequence GTX314L gets more certain and more correct power reset function than any others.

The external reset using NRST pin is activated during low input pulse. The intensive system reset can be easily obtained by this low pulse input to the NRST pin. More than 10usec low pulse period is required for proper reset. Because NRST pin has an internal pull-up resistor (typical value is  $30K\Omega$ ), the NRST pin might be floating.

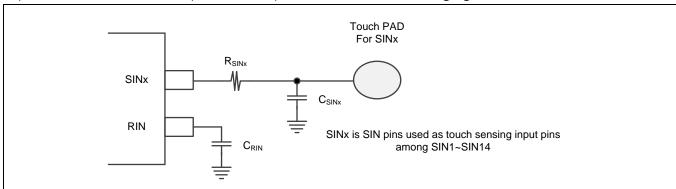

#### 8.2 IMPLEMENTATION FOR TOUCH SENSING (SIN1 ~ SIN14, RIN)

SIN inputs (SIN1~SIN14) and RIN input are used for touch detection of capacitance variation sensing. The SIN input pins are connected to touch sensing pad and catches capacitance variation caused by direct touch or approach. And RIN input for the reference capacitance is connected to a capacitor and resistor to compensate capacitance difference between SIN inputs and RIN input. The GTX314L compares each capacitance of SIN input and that of RIN input and determines touch detection of each channel when capacitance of each SIN input increases. So, for correct capacitance comparison between SIN inputs and RIN input, approximately equal initial-steady state capacitance between SIN inputs and RIN input are recommended. User can compensate initial-steady state capacitance difference between SIN inputs and RIN input by adding capacitor to RIN pin.

The GTX314L also has various intelligent sensing functions to determine valid touch from error or sensitivity problems caused by various environmental noise effects. These advanced sensing methods will help making faultless touch key systems under the worst conditions.

The internal intelligent sensitivity adjustment algorithm removes sensitivity rolling caused by system noise, circuit deviation, and circumstantial drift. The GTX314L has a special noise elimination filter for more powerful noise rejection and it will be very helpful for proper touch operation even if the system operates under deteriorative environment conditions.

The GTX314L SIN inputs have an internal series resistor for ESD protection. The additional external series resistors are profitable for prevention of abnormal actions caused by radiation noise or electrical surge pulse. In any case, if the additional external series resistor ( $R_{SIN1\sim14}$ ) of each SIN input is required, then it should be less than 1.5K $\Omega$  to SIN and the location of resister is recommended as closer to the SIN pins. For  $C_{SIN1\sim14}$ ,  $C_{RIN}$  capacitor, less than 50pF capacitor can be used.

The SIN input routing lines are desirable to be routed as short as possible and the width of routing lines should be as narrow as possible and should be placed on bottom metal. In other words, a touch PAD and other parts should be placed on different metal each other. The additional extension line pattern of RIN input on application PCB can help prevention of abnormal actions caused by radiation noise, but excessive long RIN input line can be a reason for failure of touch detect. The SIN inputs and RIN input lines are desirable to be routed as far as possible from impedance varying path such as LED drive current path. All touch sensing pads are recommended to be surrounded by GND pattern in order to reduce noise influence.

Implementation circuit for SIN pins and RIN pin is shown in the following figure.

#### 8.3 IMPLEMENTATION FOR INTERRUPT (INT)

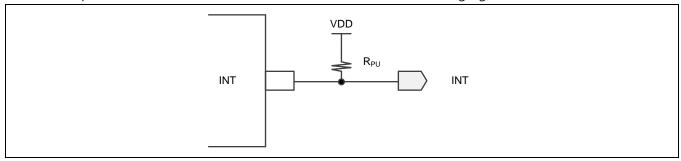

The GTX314L provides an interrupt (INT) function to reduce a communication load between MCU and GTX314L. The INT will indicate a point of time that the output status registers at the address 02h and 03h changes and MCU needs to read it. The INT pin has an open drain NMOS structure hence a couple of  $k\Omega$  pull-up resistor must be required.

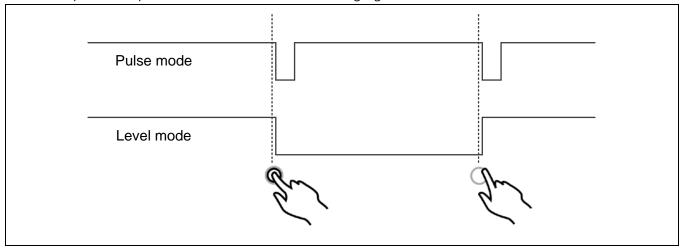

(See register address 10h = INT\_MODE)

The basic implementations for active low modes are shown in the following figure.

Two interrupt mode operations are shown in the following figure.

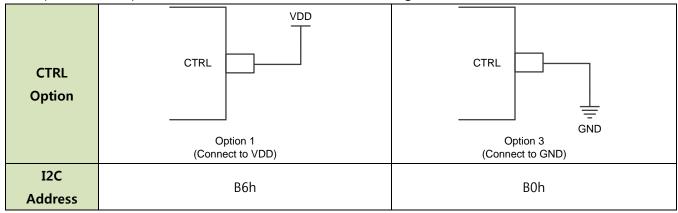

#### 8.4 CTRL OPTION SELECTION (CTRL)

In the GTX314L, three options are available by CTRL pin connection. Each option and its connections are shown in the table and figures below. This CTRL pulse signal starts at internal power reset time and finishes after a few operation period and options setting. For more detail sensitivity adjustment, C<sub>SIN</sub> capacitors should be used.

Each options and respective connection are shown in the following table.

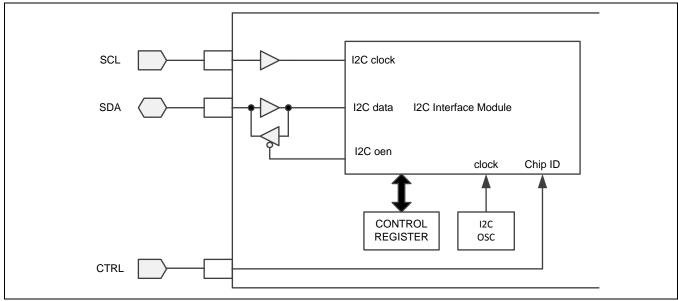

#### 8.5 I2C INTERFACE (SCL, SDA, CTRL)

The I2C-bus is for 2-way, 2-line communication between different ICs or modules. The serial bus consists of two bidirectional lines; one for data signals (SDA), and one for clock signals (SCL).

Both the SDA and SCL lines be connected to a positive supply voltage via a internal pull-up resistor (typical  $10k\Omega$ ) to prevent open gate leakage current in input mode. But the lines must be connected to a positive supply voltage via a pull-up additional external resistor.

The internal oscillator is disabled when all of both the SDA and SCL lines are high for saving current consumption.

The simple internal block diagram for SCL and SDA is shown in the following figure.

#### 8.5.1 DEVICE ADDRESSING

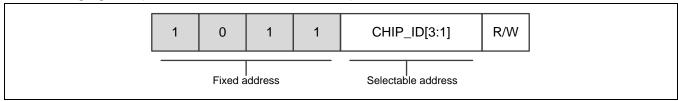

Following a START condition, the bus master must output the address of the slave it is accessing. To conserve power, no internal pull-up resistors are incorporated on the hardware selectable pins(CTRL) and it must be connected to VDD or GND.

The last bit of the slave address defines the operation to be performed. When set to logic 1, a read operation is selected, while a logic 0 selects a write operation.

The following figure represents the I2C slave address map.

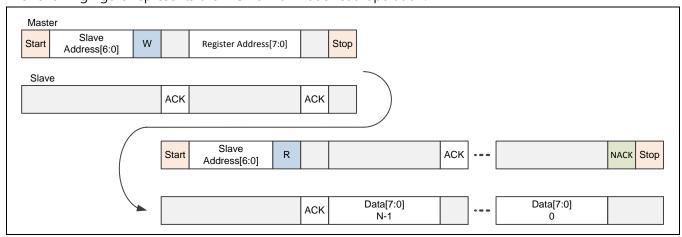

#### 8.5.2 READ OPERATION

The following figure represents the I2C normal mode read operation.

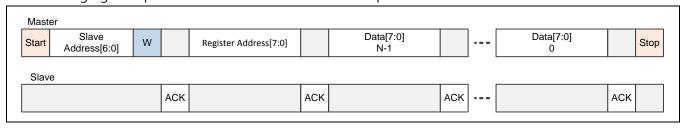

#### 8.5.3 WRITE OPERATION

The following figure represents the I2C normal mode write operation.

# 9. REGISTER DESCRIPTION

## 9.1 QUICK REGISTER MAP

| 0 -1 -1 | D AA   | Reset<br>Value | Data   |           |        |           |           |             |        |                |        |        |       |

|---------|--------|----------------|--------|-----------|--------|-----------|-----------|-------------|--------|----------------|--------|--------|-------|

| Address | R/W    |                | Bit7   | Bit6      | Bit5   | Bit4      | Bit3      | Bit2        | Bit1   | Bit0           |        |        |       |

| 00h     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 01h     | R/W    | B6h<br>B0h     | 1      | 0         | 1      | 1         | (         | CHIP_ID[3:1 | .]     | 0              |        |        |       |

| 02h     | R      |                | _      | TOUCH_    | TOUCH_ | TOUCH_    | TOUCH_    | TOUCH_      | TOUCH_ | TOUCH_         | TOUCH_ |        |       |

| 0211    | N      | K -            | OUT8   | OUT7      | OUT6   | OUT5      | OUT4      | OUT3        | OUT2   | OUT1           |        |        |       |

| 03h     | P      | R -            | 0      | 0         | TOUCH_ | TOUCH_    | TOUCH_    | TOUCH_      | TOUCH_ | TOUCH_         |        |        |       |

| 0311    | IX.    | _              | U      | 0         | OUT14  | OUT13     | OUT12     | OUT11       | OUT10  | OUT9           |        |        |       |

| 04h     | n R/W  | FFh            | SIN8_  | SIN7_     | SIN6_  | SIN5_     | SIN4_     | SIN3_       | SIN2_  | SIN1_          |        |        |       |

| 0411    | 11/ 44 | 1111           | CH_EN  | CH_EN     | CH_EN  | CH_EN     | CH_EN     | CH_EN       | CH_EN  | CH_EN          |        |        |       |

| 05h     | R/W    | R/M/           | R /\\/ | D \/V\ 31 | 3Fh    | 0         | 0         | SIN14_      | SIN13_ | SIN12_         | SIN11_ | SIN10_ | SIN9_ |

| 0311    |        | 3111           |        |           | CH_EN  | CH_EN     | CH_EN     | CH_EN       | CH_EN  | CH_EN          |        |        |       |

| 06h     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 07h     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 08h     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 09h     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 0Ah     | R/W    | 31h            | 0      | 0         | 1      | 1         | 0         | 0           | 0      | MON_<br>RST    |        |        |       |

| 0Bh     | R/W    | 00h            | 0      | 0         | 0      | 0         | 0         | 0           | 0      | SOFT_<br>RST   |        |        |       |

| 0Ch     | R/W    | 00h            | 0      | 0         | 0      | 0         | 0         | 0           | 0      | I2C_<br>PU_DIS |        |        |       |

| 0Dh     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 0Eh     |        |                |        |           |        |           |           |             |        |                |        |        |       |

| 0Fh     | R/W    | 5Ah            |        |           | R      | EGISTER_V | VRITE_LOC | K           |        |                |        |        |       |

**NOTE:** The blank register is assigned FFh data.

| A 1.1   | D 04/ | Reset |      |      |          | Da           | ıta                  |         |           |                |

|---------|-------|-------|------|------|----------|--------------|----------------------|---------|-----------|----------------|

| Address | R/W   | Value | Bit7 | Bit6 | Bit5     | Bit4         | Bit3                 | Bit2    | Bit1      | Bit0           |

| 10h     | R/W   | 11h   | 0    | 0    | 0        | INT_<br>MODE | 0                    | 0       | 0         | MULTI_<br>MODE |

| 11h     | R/W   | 32h   | 0    |      | EXP_TIME |              | 0                    | 0       | EXP_EN    | EXP_<br>MODE   |

| 12h     |       |       |      |      |          |              |                      |         |           |                |

| 13h     | R/W   | 0Ah   | 0    | 0    | 0        | 0            |                      | CAL_    | TIME      |                |

| 14h     | R/W   | 00h   | 0    | 0    | 0        | 0            |                      | SEN_IDI | LE_TIME   |                |

| 15h     | R/W   | 01h   | 0    | 0    | 0        | 0            | SEN_IDLE_TIME_SUFFIX |         |           | X              |

| 16h     |       |       |      |      |          |              |                      |         |           |                |

| 17h     | R/W   | 03h   | 0    | 0    | 0        | 0            | 0                    | BUSY    | _TO_IDLE_ | TIME           |

| 18h     | R/W   | 00h   | 0    | 0    | 0        | 0            | 0                    | 0       | 0         | i2B_<br>MODE   |

| 19h     | R/W   | 00h   | 0    | 0    | 0        | 0            | 0                    | 0       | 0         | SLIDE<br>_MODE |

| 1Ah     |       |       |      |      |          |              |                      |         |           |                |

| 1Bh     |       |       |      |      |          |              |                      |         |           |                |

| 1Ch     |       |       |      |      |          |              |                      |         |           |                |

| 1Dh     |       |       |      |      |          |              |                      |         |           |                |

| 1Eh     |       |       |      |      |          |              |                      |         |           |                |

| 1Fh     |       |       |      |      |          |              |                      |         |           |                |

**NOTE:** The blank register is assigned FFh data.

| A 1.1   | D 04/   | Reset |      |      |                           | Da   | nta    |         |      |      |  |

|---------|---------|-------|------|------|---------------------------|------|--------|---------|------|------|--|

| Address | R/W     | Value | Bit7 | Bit6 | Bit5                      | Bit4 | Bit3   | Bit2    | Bit1 | Bit0 |  |

| 20h     |         |       | 0    | 0    |                           |      |        |         |      |      |  |

| 21h     |         |       | 0    | 0    |                           |      | SENSI  | TIVITY2 |      |      |  |

| 22h     |         |       | 0    | 0    |                           |      | SENSI  | TIVITY3 |      |      |  |

| 23h     |         |       | 0    | 0    |                           |      | SENSI  | TIVITY4 |      |      |  |

| 24h     |         | -     | 0    | 0    |                           |      | SENSI  | TIVITY5 |      |      |  |

| 25h     |         |       | 0    | 0    | SENSITIVITY6 SENSITIVITY7 |      |        |         |      |      |  |

| 26h     | D // // | ٥٢١-  | 0    | 0    |                           |      |        |         |      |      |  |

| 27h     | R/W     | 0Fh   | 0    | 0    |                           |      | SENSI  | TIVITY8 |      |      |  |

| 28h     |         |       | 0    | 0    |                           |      | SENSI  | TIVITY9 |      |      |  |

| 29h     |         |       | 0    | 0    |                           |      | SENSIT | TVITY10 |      |      |  |

| 2Ah     |         |       | 0    | 0    |                           |      | SENSIT | TVITY11 |      |      |  |

| 2Bh     |         |       | 0    | 0    | SENSITIVITY12             |      |        |         |      |      |  |

| 2Ch     |         |       | 0    | 0    | SENSITIVITY13             |      |        |         |      |      |  |

| 2Dh     |         |       | 0    | 0    | SENSITIVITY14             |      |        |         |      |      |  |

| 2Eh     |         |       |      |      |                           |      |        |         |      |      |  |

| 2Fh     |         |       |      |      |                           |      |        |         |      |      |  |

**NOTE:** The blank register is assigned FFh data.

#### 9.2 REGISTER CONFIGURATION

#### **9.2.1 01H REGISTER**

| Address | R/W    | Reset              | Data |      |      |      |              |      |      |      |  |

|---------|--------|--------------------|------|------|------|------|--------------|------|------|------|--|

| Address | IX) VV | Value              | Bit7 | Bit6 | Bit5 | Bit4 | Bit3         | Bit2 | Bit1 | Bit0 |  |

|         | R/W,   |                    | 1    | 0    | 1    | 1    | CHIP_ID[3:1] |      |      | 0    |  |

| 01h     |        | B6h <sup>(1)</sup> | 1    | 0    | 1    | 1    | 0            | 1    | 1    | 0    |  |

|         |        | B0h <sup>(3)</sup> | 1    | 0    | 1    | 1    | 0            | 0    | 1    | 0    |  |

| CHIP_ID[3:1] | Hardware selectable chip ID bit                 |

|--------------|-------------------------------------------------|

|              | CTRL pin = VDD, CHIP_ID[3:1] = 011              |

|              | CTRL pin = GND, CHIP_ID[3:1] = 000              |

|              | NOTE: This bit might be controlled by CTRL pin. |

NOTE: (1) CTRL pin = VDD, (2) CTRL pin = GND

#### 9.2.2 02H, 03H REGISTER

| 0 al al a a | D AM | Reset | Data   |        |        |        |        |        |        |        |  |

|-------------|------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|

| Address     | R/W  | Value | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |  |

| 02h         | R    |       | TOUCH_ |  |

| 0211        |      | -     | OUT8   | OUT7   | OUT6   | OUT5   | OUT4   | OUT3   | OUT2   | OUT1   |  |

| 03h         | R -  | -     | - 0    | 0      | TOUCH_ | TOUCH_ | TOUCH_ | TOUCH_ | TOUCH_ | TOUCH_ |  |

| 0311        |      |       |        |        | OUT14  | OUT13  | OUT12  | OUT11  | OUT10  | OUT9   |  |

| TOUCH_OUTn(1) | Each of SIN touch detection status bit         |

|---------------|------------------------------------------------|

|               | 0 = No touch detection                         |

|               | 1 = Touch detection.                           |

|               | NOTE: It's set '1' when touch detection occur. |

**NOTE:** (1)  $n = SIN1 \sim SIN14$  pin

#### 9.2.3 04H, 05H REGISTER

| Adduses | R/W | Reset | Data  |       |       |        |        |        |        |        |       |

|---------|-----|-------|-------|-------|-------|--------|--------|--------|--------|--------|-------|

| Address |     | Value | Bit7  | Bit6  | Bit5  | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |       |

|         |     |       | SIN8_ | SIN7_ | SIN6_ | SIN5_  | SIN4_  | SIN3_  | SIN2_  | SIN1_  |       |

| 04h     | R/W |       | CH_EN | CH_EN | CH_EN | CH_EN  | CH_EN  | CH_EN  | CH_EN  | CH_EN  |       |

|         |     | FFh   | 1     | 1     | 1     | 1      | 1      | 1      | 1      | 1      |       |

|         | R/W |       |       | 0     | 0     | SIN14_ | SIN13_ | SIN12_ | SIN11_ | SIN10_ | SIN9_ |

| 05h     |     |       | U     | U     | CH_EN | CH_EN  | CH_EN  | CH_EN  | CH_EN  | CH_EN  |       |

|         |     | 3Fh   | 0     | 0     | 1     | 1      | 1      | 1      | 1      | 1      |       |

| SINn <sup>(1)</sup> _CH_EN | Each of channel(SIN1~14) enable/disable bits                                                         |

|----------------------------|------------------------------------------------------------------------------------------------------|

|                            | 0 = disable                                                                                          |

|                            | 1 = enable                                                                                           |

|                            | <b>NOTE:</b> It's configured with the new offset when the SINn <sup>(1)</sup> _CH_EN bit is enabled. |

**NOTE:** (1)  $n = SIN1 \sim SIN14 pin$

#### 9.2.4 OAH REGISTER

| Address R/W | D /// | Reset | Data |      |      |      |      |      |      |      |  |

|-------------|-------|-------|------|------|------|------|------|------|------|------|--|

|             | Value | Bit7  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |      |  |

|             |       |       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | MON_ |  |

| 0Ah         | R/W   |       | U    | U    | U    | U    | U    | U    | U    | RST  |  |

|             |       | 31h   | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    |  |

| MON_RST | Internal and external reset monitoring bit  0 = not active and clear bit by user  1 = active and set bit by GTX314L |

|---------|---------------------------------------------------------------------------------------------------------------------|

|         | NOTE: It's set '1' when GTX314L is reset.                                                                           |

#### 9.2.5 OBH REGISTER

| Address R/W | D AM  | Reset | Reset Data |      |      |      |      |      |      |       |

|-------------|-------|-------|------------|------|------|------|------|------|------|-------|

|             | Value | Bit7  | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |       |

|             |       |       | 0          | 0    | 0    | 0    | 0    | 0    | 0    | SOFT_ |

| 0Bh         | R/W   |       | U          | U    | U    | U    | U    | U    | U    | RST   |

|             |       | 00h   | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

| SOFT_RST | Soft reset bit                                                                                                       |

|----------|----------------------------------------------------------------------------------------------------------------------|

|          | 0 = Operation mode                                                                                                   |

|          | 1 = Sleep mode.                                                                                                      |

|          | NOTE: Current consumption can be saved and Touch engine is not work in sleep mode.                                   |

|          | <b>NOTE:</b> It's configured with the new offset when the SOFT_RST bit is changed from sleep mode to operation mode. |

|          | NOTE: All the value of register are not changed by SOFT_RST bit.                                                     |

#### 9.2.6 OCH REGISTER

| Address R/W | D /// | Reset                               | Data |   |   |   |   |   |   |        |   |   |   |      |

|-------------|-------|-------------------------------------|------|---|---|---|---|---|---|--------|---|---|---|------|

|             | Value | Value Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 |      |   |   |   |   |   |   |        |   |   |   |      |

|             |       |                                     |      |   |   |   | 0 | 0 | 0 | 0      | 0 | 0 | 0 | I2C_ |

| 0Ch         | R/W   |                                     | U    | U | U | U | U | U | U | PU_DIS |   |   |   |      |

|             |       | 00h                                 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0      |   |   |   |      |

| I2C_PU_DIS | I2C pull-up control bit |

|------------|-------------------------|

|            | 0 = I2C pull-up enable  |

|            | 1 = I2C pull-up disable |

#### 9.2.7 OFH REGISTER

| Address | D /// | Reset |      |      |      | Da        | ıta       |      |      |      |

|---------|-------|-------|------|------|------|-----------|-----------|------|------|------|

| Address | R/W   | Value | Bit7 | Bit6 | Bit5 | Bit4      | Bit3      | Bit2 | Bit1 | Bit0 |

| OFL DAA | R/W   |       |      |      | R    | EGISTER_V | VRITE_LOC | K    |      |      |

| 0Fh     | K/VV  | 5Ah   | 0    | 1    | 0    | 1         | 1         | 0    | 1    | 0    |

| REGISTER_WRITE_LOCK | Register write lock bit                                                         |

|---------------------|---------------------------------------------------------------------------------|

|                     | 5Ah = All of registers can be read and write.                                   |

|                     | Other = All of registers are locked. But it's possible to read registers.       |

|                     | NOTE: When I2C is not used to write operation, it is recommended to prevent the |

|                     | write operation by using the "REGISTER_WRITE_LOCK" function.                    |

#### **9.2.8 10H REGISTER**

| Address R/W | Reset |      |      | Data |      |      |      |      |      |      |        |

|-------------|-------|------|------|------|------|------|------|------|------|------|--------|

|             | Value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |      |        |

|             |       |      |      |      |      | 0    | INT_ | 0    | 0    | 0    | MULTI_ |

| 10h         | R/W   |      | U    | U    | U    | MODE | U    | U    | U    | MODE |        |

|             |       | 11h  | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    |        |

| INT_MODE   | Interrupt operation mode selection bit |

|------------|----------------------------------------|

|            | 0 = Pulse mode.                        |

|            | 1 = Level mode.                        |

| MULTI_MODE | Touch engine mode selection bit        |

|            | 0 = Single touch mode                  |

|            | 1 = Multi touch mode.                  |

#### **9.2.9 11H REGISTER**

| Adduses | D ///       | Reset | et Data |      |          |      |      |      |        |      |  |

|---------|-------------|-------|---------|------|----------|------|------|------|--------|------|--|

| Address | Address R/W | Value | Bit7    | Bit6 | Bit5     | Bit4 | Bit3 | Bit2 | Bit1   | Bit0 |  |

| 111     |             |       | 0       |      | EXP_TIME |      | 0    | 0    | EXP_EN | EXP_ |  |

| 11h     | R/W         |       |         |      |          |      |      |      |        | MODE |  |

|         |             | 32h   | 0       | 0    | 1        | 1    | 0    | 0    | 1      | 0    |  |

| EXP_TIME <sup>(1)</sup> | Touch expire time selection bit              |                                           |  |  |  |  |  |  |  |

|-------------------------|----------------------------------------------|-------------------------------------------|--|--|--|--|--|--|--|

|                         | 000 = 5sec                                   | 100 = 25sec                               |  |  |  |  |  |  |  |

|                         | 001 = 10sec                                  | 101 = 30sec                               |  |  |  |  |  |  |  |

|                         | 010 = 15sec                                  |                                           |  |  |  |  |  |  |  |

|                         | 011 = 20sec                                  |                                           |  |  |  |  |  |  |  |

| EXP_EN                  | Touch expire enable bit                      |                                           |  |  |  |  |  |  |  |

|                         | 0 = disable                                  |                                           |  |  |  |  |  |  |  |

|                         | 1 = enable                                   |                                           |  |  |  |  |  |  |  |

|                         | NOTE: It's configured with the new offset wh | en the touch expire function is executed. |  |  |  |  |  |  |  |

| EXP_MODE                | Touch expire mode bit                        |                                           |  |  |  |  |  |  |  |

|                         | 0 = expire count is not restarted wheneve    | r a different touch occurs                |  |  |  |  |  |  |  |

|                         | 1 = expire count is restarted if a different | touch occur                               |  |  |  |  |  |  |  |

#### 9.2.10 13H REGISTER

| Address R/ | D /// | Reset Value | Data |      |      |      |      |      |      |      |  |

|------------|-------|-------------|------|------|------|------|------|------|------|------|--|

|            | K/ VV |             | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

| 121 0.04   | D AM  |             | 0    | 0    | 0    | 0    |      | CAL_ | TIME |      |  |

| 13h        | R/W   | 0Ah         | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    |  |

| CAL_TIME <sup>(1)</sup> | Calibration time selection bit               |                            |

|-------------------------|----------------------------------------------|----------------------------|

|                         | 0000 = 0msec + 1 period                      | 1000 = 800msec + 1 period  |

|                         | 0001 = 100msec + 1 period                    | 1001 = 900msec + 1 period  |

|                         | 0010 = 200msec + 1 period                    | 1010 = 1000msec + 1 period |

|                         | 0011 = 300msec + 1 period                    | 1011 = 1100msec + 1 period |

|                         | 0100 = 400msec + 1 period                    | 1100 = 1200msec + 1 period |

|                         | 0101 = 500msec + 1 period                    | 1101 = 1300msec + 1 period |

|                         | 0110 = 600msec + 1 period                    | 1110 = 1400msec + 1 period |

|                         | 0111 = 700msec + 1 period                    | 1111 = No Calibration      |

|                         | NOTE:                                        |                            |

|                         | (1) The calibration time to protect from env | rironmental change         |

|                         | (2) Deviation: ±30% (@5.0V)                  |                            |

#### 9.2.11 14H REGISTER

| Address | R/W  | Reset |      | Data |      |      |      |         |         |      |  |

|---------|------|-------|------|------|------|------|------|---------|---------|------|--|

|         |      | Value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2    | Bit1    | Bit0 |  |

| 141     | D AM |       | 0    | 0    | 0    | 0    |      | SEN_IDI | _E_TIME |      |  |

| 14h     | R/W  | 00h   | 0    | 0    | 0    | 0    | 0    | 0       | 0       | 0    |  |

| SEN_IDLE_TIME(1) | Idle time section bit                                      |                         |                |                |  |  |  |  |  |

|------------------|------------------------------------------------------------|-------------------------|----------------|----------------|--|--|--|--|--|

|                  | 0000= 1msec                                                | 0100= 400msec           | 1000= 800msec  | 1100= 1200msec |  |  |  |  |  |

|                  | 0001= 100msec                                              | 0101= 500msec           | 1001= 900msec  | 1101= 1300msec |  |  |  |  |  |

|                  | 0010= 200msec                                              | 0110= 600msec           | 1010= 1000msec | 1110= 1400msec |  |  |  |  |  |

|                  | 0011= 300msec                                              | 0111= 700msec           | 1011= 1100msec | 1111= 1500msec |  |  |  |  |  |

|                  | NOTE: The idle time                                        | equation is as follows. |                |                |  |  |  |  |  |

|                  | IDLE_TIME = SEN_IDLE_TIME[3:0] + SEN_IDLE_TIME_SUFFIX[3:0] |                         |                |                |  |  |  |  |  |

|                  | Ex> 110msec = 100ms                                        | ec + 10msec             |                |                |  |  |  |  |  |

**NOTE:** (1) Test condition: VDD = 3.0V, TA =  $25^{\circ}C$

#### 9.2.12 15H REGISTER

| Address  | D ///  | Reset | Reset Data |      |      |      |                      |      |      |      |  |

|----------|--------|-------|------------|------|------|------|----------------------|------|------|------|--|

|          | R/W    | Value | Bit7       | Bit6 | Bit5 | Bit4 | Bit3                 | Bit2 | Bit1 | Bit0 |  |

| 151 0.04 | D /\A/ |       | 0          | 0    | 0    | 0    | SEN_IDLE_TIME_SUFFIX |      |      |      |  |

| 15h      | R/W    | 01h   | 0          | 0    | 0    | 0    | 0                    | 0    | 0    | 1    |  |

| SEN_IDLE_TIME_SUFFIX(1) | Idle time suffix sec | ction bit                                                  |               |               |  |  |  |  |  |

|-------------------------|----------------------|------------------------------------------------------------|---------------|---------------|--|--|--|--|--|

|                         | 0000= 0msec          | 0100= 40msec                                               | 1000= 80msec  | 1100= 120msec |  |  |  |  |  |

|                         | 0001= 10msec         | 0101= 50msec                                               | 1001= 90msec  | 1101= 130msec |  |  |  |  |  |

|                         | 0010= 20msec         | 0110= 60msec                                               | 1010= 100msec | 1110= 140msec |  |  |  |  |  |

|                         | 0011= 30msec         | 0111= 70msec                                               | 1011= 110msec | 1111= 150msec |  |  |  |  |  |

|                         |                      | ne equation is as follo                                    |               |               |  |  |  |  |  |

|                         | IDLE_TIME = SEN_ID   | IDLE_TIME = SEN_IDLE_TIME[3:0] + SEN_IDLE_TIME_SUFFIX[3:0] |               |               |  |  |  |  |  |

|                         | Ex> 110msec = 100    | msec + 10msec                                              |               |               |  |  |  |  |  |

#### 9.2.13 17H REGISTER

| Address R/W | D /// | Reset | Data |      |      |      |      |      |            |      |  |

|-------------|-------|-------|------|------|------|------|------|------|------------|------|--|

|             | K/ VV | Value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1       | Bit0 |  |

| 176         | D AA  |       | 0    | 0    | 0    | 0    | 0    | BUSY | _TO_IDLE_T | IME  |  |

| 17h         | R/W   | 03h   | 0    | 0    | 0    | 0    | 0    | 0    | 1          | 1    |  |

| BUSY_TO_IDLE_TIME(1) | Busy to Idle time selection bit |           |

|----------------------|---------------------------------|-----------|

|                      | 000 = 0sec (disable)            | 100= 4sec |

|                      | 001 = 1sec                      | 101= 5sec |

|                      | 010 = 2sec                      | 110= 6sec |

|                      | 011 = 3sec                      | 111= 7sec |

#### 9.2.14 18H REGISTER

| A dalueses | D /// | Reset | Data |      |      |      |      |      |      |      |  |  |

|------------|-------|-------|------|------|------|------|------|------|------|------|--|--|

| Address    | R/W   | Value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|            |       |       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | I2B_ |  |  |

| 18h        | R/W   |       | U    | U    | U    | 0    | U    | U    | 0    | MODE |  |  |

|            |       | 00h   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| I2B_MODE | Idle to busy mode control bit |

|----------|-------------------------------|

|          | 0 = auto mode                 |

|          | 1 = manual mode               |

#### 9.2.15 19H REGISTER

| A al alva a a | D AM | Reset | Data |      |      |      |      |      |      |       |       |

|---------------|------|-------|------|------|------|------|------|------|------|-------|-------|

| Address R/V   | R/W  | Value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  |       |

| 19h R/W       |      |       |      | 0    | 0    | 0    | 0    | 0    | 0    | 0     | SLIDE |

|               | R/W  |       | U    | U    | U    | U    | U    | U    | U    | _MODE |       |

|               |      | 00h   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     |       |

| SLIDE_MODE | Slide mode enable bit |

|------------|-----------------------|

|            | 0 = disable           |

|            | 1 = enable            |

#### 9.2.16 20H~2DH REGISTER

| 0 -1 -1 | D AM | Reset |      |      |               | Da   | ıta    |         |      |      |

|---------|------|-------|------|------|---------------|------|--------|---------|------|------|

| Address | R/W  | Value | Bit7 | Bit6 | Bit5          | Bit4 | Bit3   | Bit2    | Bit1 | Bit0 |

|         |      |       | 0    | 0    |               |      | SENSIT | TVITY1  |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | TVITY2  |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | TVITY3  |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | TVITY4  |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | TVITY5  |      |      |

|         |      |       | 0    | 0    | SENSITIVITY6  |      |        |         |      |      |

| 20h     |      |       | 0    | 0    | SENSITIVITY7  |      |        |         |      |      |

| ~       | R/W  |       | 0    | 0    |               |      | SENSIT | TVITY8  |      |      |

| 2Dh     |      |       | 0    | 0    |               |      | SENSIT | TVITY9  |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | IVITY10 |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | IVITY11 |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | IVITY12 |      |      |

|         |      |       | 0    | 0    | SENSITIVITY13 |      |        |         |      |      |

|         |      |       | 0    | 0    |               |      | SENSIT | IVITY14 |      |      |

|         |      | 0Fh   | 0    | 0    | 0             | 0    | 1      | 1       | 1    | 1    |

| SENSITIVITYn(1) | Touch sensitivity control bit                                                   |

|-----------------|---------------------------------------------------------------------------------|

|                 | 03h = Very high sensitive                                                       |

|                 | 3Fh = Very high insensitive                                                     |

|                 | <b>NOTE:</b> It's recommended to use 0Ch~3Fh values at the sensitivity setting. |

**NOTE:** (1)  $n = SIN1 \sim SIN14$  pin

# 10. ELECTRICAL CHARACTERISTICS

#### **10.1 ABSOLUTE MAXIMUM RATINGS**

| Parameter                           | Symbol              | Conditions | Min  | Тур. | Max  | Units      |

|-------------------------------------|---------------------|------------|------|------|------|------------|

| Maximum supply voltage              | V <sub>DD_MAX</sub> |            | -0.3 |      | 6.0  | V          |

| Supply voltage range <sup>(1)</sup> | V <sub>DD_RNG</sub> |            | -0.3 |      | 6.0  | V          |

| Voltage on any input pin            | W                   |            | -0.3 |      | VDD  | V          |

| Voltage on any input pin            | V <sub>IN_MAX</sub> |            | -0.5 |      | +0.3 | V          |

| Maximum current into any pin        | I <sub>MIO</sub>    |            | -100 |      | 100  | mA         |

| Power dissipation                   | P <sub>MAX</sub>    |            | -    |      | 800  | mW         |

| Storage temperature                 | T <sub>STG</sub>    |            | -65  |      | 150  | $^{\circ}$ |

| Operating humidity                  | H <sub>OP</sub>     | 8 hours    | 5    |      | 95   | %          |

| Operating temperature               | T <sub>OPR</sub>    |            | -40  |      | 85   | $^{\circ}$ |

| Junction temperature                | TJ                  |            | -40  |      | 125  | $^{\circ}$ |

**NOTE:** (1) This is the real valid power supply voltage range considering allowable supply tolerance. It cannot be used as target supply voltage range which is separately presented at below I/O ELECTRICAL CHRACTERISTICS.

#### 10.2 I/O ELECTRICAL CHARACTERISTICS

This section includes information about power supply requirements and I/O pin characteristics.

(TA = -25 to 85°C,  $V_{DD}$  = 1.8V to 5.5V)

| Parameter                          | Symbol            | Conditions                                                                                | Min.   | Тур.      | Max.   | Unit |

|------------------------------------|-------------------|-------------------------------------------------------------------------------------------|--------|-----------|--------|------|

| Target supply voltage              | $V_{DD}$          |                                                                                           | 1.8    | 3.0 / 5.0 | 5.5    | V    |

| Current consumption                | I <sub>DD</sub>   | Standby mode @IDLE_TIME=200msec <sup>(1)</sup> @SENSING_CNT=3,000cnt <sup>(2)</sup>       | -      | 18        | -      | uA   |

|                                    | (VDD=3.0V)        | Standby mode @IDLE_TIME=200msec <sup>(1)</sup> @SENSING_CNT=2,000cnt <sup>(3)</sup>       | -      | 16        | ı      | uA   |

|                                    | I <sub>DD</sub>   | Standby mode<br>@IDLE_TIME=200msec <sup>(1)</sup><br>@SENSING_CNT=3,000cnt <sup>(2)</sup> | -      | 32        | -      | uA   |

|                                    | (VDD=5.0V)        | Standby mode<br>@IDLE_TIME=200msec <sup>(1)</sup><br>@SENSING_CNT=2,000cnt <sup>(3)</sup> | -      | 29        | ı      | uA   |

| Input high voltage                 | V <sub>IH</sub>   | All input pins                                                                            | 0.7VDD | -         | VDD    | V    |

|                                    |                   |                                                                                           |        |           | + 0.3  |      |

| Input low voltage                  | V <sub>IL</sub>   | All input pins                                                                            | -0.3   | -         | 0.3VDD | V    |

| Output low voltage                 | V <sub>VOL</sub>  | All output pins                                                                           | -      | -         | 0.4    | V    |

|                                    |                   | (I <sub>OL</sub> = 10mA,                                                                  |        |           |        |      |

|                                    |                   | VDD = 5.0V)                                                                               |        |           |        |      |

| Output sink current <sup>(4)</sup> | I <sub>SINK</sub> | All output pins                                                                           | -      | -         | 10     | mA   |

|                                    |                   | (Active low)                                                                              | _      |           |        |      |

| Output high leakage current        | I <sub>LOH</sub>  |                                                                                           | -      | -         | 1      | uA   |

| NRST internal pull-up<br>resister <sup>(4)</sup> | R <sub>PU_RST</sub> | - | 30 | - | kΩ |

|--------------------------------------------------|---------------------|---|----|---|----|

| SDA Internal Pull-up<br>Resister <sup>(4)</sup>  | R <sub>PU_SDA</sub> | - | 30 | - | kΩ |

| SCL Internal Pull-up<br>Resister <sup>(4)</sup>  | R <sub>PU_SCL</sub> | - | 30 | - | kΩ |

#### NOTE:

- (1) refer to address=14h(SEN\_IDLE\_TIME) and address=15h(SEN\_IDLE\_TIME\_SUFFIX) registers

- (2) SENSING\_CNT=3,000cnt register configuration address 40h=04h, address 41h=02h, address 42h=02h, address 43h=01h address 44h=00h, address 45h=03h, address 46h=00h, address 47h=00h

- (3) SENSING\_CNT=2,000cnt register configuration address 40h=02h, address 41h=01h, address 42h=01h, address 43h=00h address 44h=02h, address 45h=03h, address 46h=00h, address 47h=02h

- (4) Test condition: VDD = 3.0V,  $TA = 25^{\circ}C$  and normal operation mode under default control register value. (Unless otherwise noted)

#### 10.3 RESET CHARACTERISTICS

$(TA = -25 \text{ to } 85^{\circ}\text{C}, V_{DD} = 1.8\text{V to } 5.5\text{V})$

| Parameter               | Symbol           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|------------------|------------|------|------|------|------|

| NRST input high width   | t <sub>RST</sub> |            | 10   | -    | -    | usec |

| POR <sup>(1)</sup> Time | t <sub>POR</sub> |            | -    | -    | 600  | usec |

| POR voltage             | V <sub>POR</sub> |            | -    | 1.5  | -    | V    |

**NOTE:** (1) POR = Internal Power-On Reset

#### 10.4 INTERRUPT OUTPUT CHARACTERISTICS

(TA = -25 to 85°C,  $V_{DD}$  = 1.8V to 5.5V)

| Parameter           | Symbol           | Conditions | Min. | Тур. | Max. | Unit |

|---------------------|------------------|------------|------|------|------|------|

| INT low pulse width | t <sub>INT</sub> |            | ı    | 5    | -    | msec |

#### 10.5 SENSING INPUT CHARACTERISTICS

(TA = -25 to 85°C,  $V_{DD}$  = 1.8V to 5.5V)

| Parameter                    | Symbol               | Conditions | Min. | Тур. | Max. | Unit |

|------------------------------|----------------------|------------|------|------|------|------|

| Minimum detectable input     | ΔC <sub>S_MIN</sub>  |            | 0.1  | -    | -    | рF   |

| capacitance variant          |                      |            |      |      |      |      |

| Maximum input                | C <sub>EXT_MAX</sub> |            | -    | -    | 50   | pF   |

| external capacitance         |                      |            |      |      |      |      |

| Sensitivity selection steps  | N <sub>SEN</sub>     |            | -    | 55   | -    | step |

| Sense OSC internal           | R <sub>INT</sub>     |            | -    | 140  | -    | Ω    |

| series resistor              |                      |            |      |      |      |      |

| external SIN series resistor | R <sub>EXT_SIN</sub> |            | -    | 560  | 1.5K | Ω    |

#### **10.6 SYSTEM CHARACTERISTICS**

(TA = -25 to 85°C,  $V_{DD}$  = 1.8V to 5.5V)

| Parameter                 | Symbol           | Conditions         | Min. | Тур. | Max. | Unit |

|---------------------------|------------------|--------------------|------|------|------|------|

| Time for stable I2C       | t <sub>I2C</sub> |                    | 1    | -    | -    | msec |

| communication after reset |                  |                    |      |      |      |      |

| Time for stable Touch     | t <sub>OP</sub>  |                    | 500  | -    | -    | msec |

| Operating after Reset     |                  |                    |      |      |      |      |

| Touch On response time    | t <sub>ON</sub>  | 1 channel Touch at | -    | 80   | -    | msec |

|                           |                  | all of register    |      |      |      |      |

|                           |                  | default            |      |      |      |      |

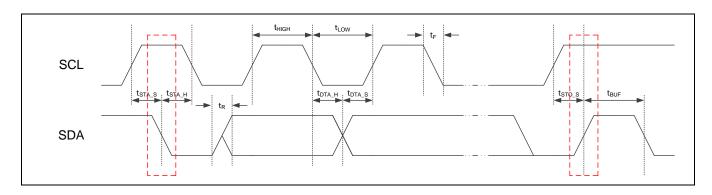

#### 10.7 I2C INTERFACE TIMING CHARACTERISTICS

$(TA = -25 \text{ to } 85^{\circ}\text{C}, V_{DD} = 1.8\text{V to } 5.5\text{V})$

| Doromotor                         | Cymph ol           | Standar | d-mode | Fast-                             | mode | l lmit |

|-----------------------------------|--------------------|---------|--------|-----------------------------------|------|--------|

| Parameter                         | Symbol             | Min.    | Max.   | Min.                              | Max. | Unit   |

| SCL clock frequency               | f <sub>SCL</sub>   | -       | 100    | -                                 | 400  | kHz    |

| Hold time for START condition     | t <sub>STA_H</sub> | 4.0     | -      | 0.6                               | -    | usec   |

| LOW period of the SCL clock       | t <sub>LOW</sub>   | 4.7     | -      | 1.3                               | 1    | usec   |

| HIGH period of the SCL clock      | t <sub>HIGH</sub>  | 4.0     | -      | 0.7                               | 1    | usec   |

| Set-up time for START condition   | t <sub>STA_S</sub> | 4.7     | -      | 0.6                               | -    | usec   |

| Data hold time                    | t <sub>DAT_H</sub> | 5       | -      | 40                                | -    | nsec   |

| Data set-up time                  | t <sub>DAT_S</sub> | 250     | -      | 100                               | -    | nsec   |

| Rise time of both SDA and SCL     | +                  |         | 1000   | 20 +                              | 300  | 2505   |

| signals                           | t <sub>R</sub>     | -       | 1000   | 0.1 C <sub>b</sub> <sup>(2)</sup> | 300  | nsec   |

| Fall time of both SDA and SCL     | +                  |         | 300    | 20 +                              | 300  | ncoc   |

| signals                           | t <sub>F</sub>     | -       | 300    | 0.1 C <sub>b</sub> <sup>(2)</sup> | 300  | nsec   |

| Set-up time for STOP condition    | t <sub>STO_S</sub> | 4.0     | -      | 0.6                               | -    | usec   |

| Bus free time between a STOP      | +                  | 4.7     |        | 1.3                               |      | LICOC  |

| and START condition               | t <sub>BUF</sub>   | 4.7     | -      | 1.5                               | -    | usec   |

| Capacitive load for each bus line | Cb                 | -       | 400    |                                   | 400  | pF     |

#### NOTE:

- $(1) \ All \ values \ referred \ to \ VIH \ and \ VIL \ levels \ (please \ refer \ to \ I/O \ ELECTRICAL \ CHRACTERISTICS).$

- (2)  $C_b$  = total capacitance of one bus line in pF.

#### **10.8 ESD CHARACTERISTICS**

Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage. During the device qualification, ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model (CDM).

| Test Mode                 | Symbol           | Test Pin    | Max   | Unit | Reference               |

|---------------------------|------------------|-------------|-------|------|-------------------------|

|                           |                  | (Reference) |       |      | Document                |

|                           |                  | VSS, I/O    | ±8000 | V    |                         |

|                           |                  | (VDD)       | 10000 | v    |                         |

| Lluman hady madal (LIRM)  | \/               | VDD, I/O    | ±8000 | V    | JS-001-2014             |

| Human body model (HBM)    | V <sub>HBM</sub> | (VSS)       | ±0000 | V    | JS-001-201 <del>4</del> |

|                           |                  | Every I/O   | ±8000 | V    |                         |

|                           |                  | (All I/O)   | ±0000 | V    |                         |

|                           |                  | VSS, I/O    | 1600  | V    |                         |

|                           |                  | (VDD)       | ±600  | V    |                         |

| Masking was del (MANA)    | \/               | VDD, I/O    | 1800  | V    | JESD22-A115C            |

| Machine model (MM)        | $V_{MM}$         | (VSS)       | ±800  | V    | :2010                   |

|                           |                  | Every I/O   | 1700  | V    |                         |

|                           |                  | (All I/O)   | ±700  | V    |                         |

| Charge device model (CDM) | \/               | Event Din   | 12000 | V    | JESD22-C101F            |

| Charge device model (CDM) | V <sub>CDM</sub> | Every Pin   | ±2000 | V    | :2013                   |

#### 10.9 LATCH-UP CHARACTERISTICS

| Test Type                                    | Symbol               | Polarity | Max  | Unit | Reference<br>Document |

|----------------------------------------------|----------------------|----------|------|------|-----------------------|

| I test                                       | I <sub>LAT_POS</sub> | Positive | 200  | mA   | JESD78E<br>- :2016    |

|                                              | I <sub>LAT_NEG</sub> | Negative | 200  | mA   |                       |

| V <sub>supply</sub> over V <sub>DD_MAX</sub> | V <sub>LAT_POS</sub> | Positive | 8.25 | V    |                       |

## 11. APPLICATION

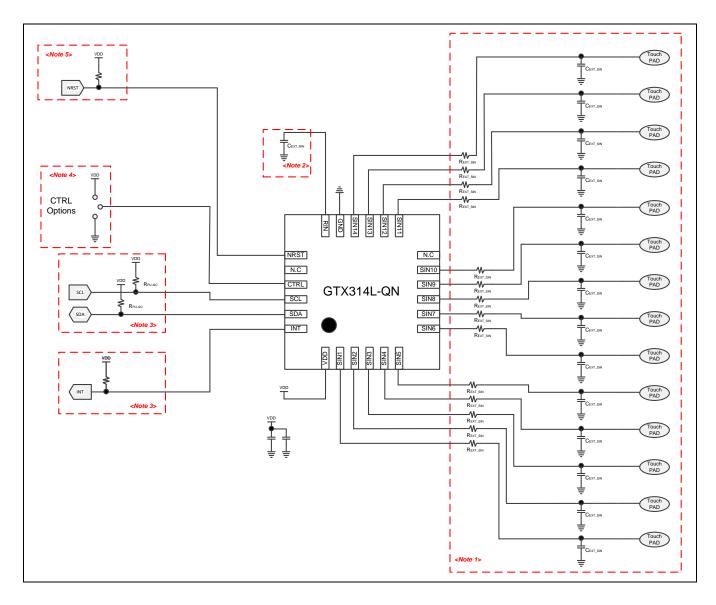

#### 11.1 EXAMPLE CIRCUIT (QFN-24L PACKAGE)

**NOTE:**  $R_{EXT\_SIN} = 560\Omega$  (recommend),  $R_{PU\_I2C} = 10K\Omega$  (recommend)

$C_{EXT\_RIN} = 4pF$  (recommend)

**NOTE:** The values of resistance and capacitance can be changed depending on the application set.

**NOTE:** It is recommended to make empty space on PCB artwork for install the capacitance later, currently even if the capacitance is not needed on the SIN ports.

#### 11.2 APPLICATION NOTES

Normally a touch sensing operation is ultimately impedance variation sensing. Hence a touch sensing system is recommended to be taken care of prevention of the external sensing disturbance. Although the GTX314L has enough noise rejection algorithms and various protection circuits to prevent error touch detection caused by noise and incapable sensing, it is better to take care in noisy applications such as home appliances. There are many measurable or invisible noises in system that can affect the impedance sensing signal or distort that signal. The main principal design issues and required attentions are such as below.

#### Power Line

- The touch sensor power line is recommended to be split from the other power lines such as relay circuits or LED power that can make pulsation noise on power lines.

- The big inductance that might exist in long power connection line can cause power fluctuation by other noise sources.

- The lower frequency periodic power noise such as a few Hz ~ kHz has more baneful influence on sensitivity calibration.

- An extra regulator for touch sensor is desirable for prevention above power line noises.

- The V<sub>DD</sub> under shooting pulse less than internal reset voltage (V<sub>DD RST</sub>) can cause system reset.

- The capacitor connected between V<sub>DD</sub> and GND is somehow obligation element for buffering above power line noises. This capacitor must be placed as near to IC as possible.

#### • Sensing (Reference) Input Line for Touch Detect <Note1><Note2>

- The sensing lines for touch detection are desirable to be routed as short as possible and the width of routing path should be as narrow as possible.

- The sensing line for touch detection should be formed by bottom metal, in other words, an opposite metal of a touch PAD.

- The additional extension line pattern of RIN input on application PCB can help prevention of abnormal actions caused by radiation noise, but excessive long RIN input line can be a reason for failure of touch detect.

- SIN capacitor is useful for sensitivity reduction adjust. A bigger capacitor of SIN makes sensitivity of corresponding channel to be lower.

- The sensing line for touch detection is desirable to be routed as far as possible from impedance varying path such as LED drive current path.

- An unused sensing channel is desirable to be turned off by control register. (Recommendation)

- Additional external series resistors are profitable for prevention of abnormal actions caused by radiation noise or electrical surge pulse. The location of resister is better as near as possible to the SIN and RIN pins for better stable operation.

- (Refer to IMPLEMENTATION FOR TOUCH SENSING)

- All touch sensing pads are recommended to be surrounded by GND pattern to reduce noise influence.

- It is recommended to be same the length and thickness of the SIN pins on PCB artwork.

#### I2C Interface and Interrupt Applications < Note3>

The SCL is I2C clock input pin and SDA is I2C data input/output pin. SCL and SDA have internal optional pull-up resistor. So, when I2C interface is not required, SCL and SDA pins can be floating. For high speed communication, SDA pin needs small pull-up resistor connected to V<sub>DD</sub> to reduce pulse rising delay.

(Refer to I2C INTERFACE)

INT is for the output signal that indicates changing of sensing output data. This pin is output only pin

and has active low function. Because INT pin has open drain structure, pull-up resistor is required for

valid output.

(Refer to IMPLEMENTATION FOR INTERRUPT)

#### CTRL Option Selection <Note4>

Three optional chip ID are available by CTRL pin connection.

(Refer to CTRL OPTION SELECTION)

#### • External Reset < Note5>

The NRST pin is for the abrupt reset input signal. The low signal pulse can make system reset. This

pin has also an internal pull-up resistor hence the NRST pin can be floating.

(Refer to INTERNAL AND EXTERNAL RESET)

# 12. PACKAGE DIMENSION (QFN-24L PACKAGE)